The following is the VHDL code for the implementation of Half Adder using Behavioral modelling.

use IEEE.STD_LOGIC_1164.ALL;

LIBRARY ieee;

wait for 100 ns;

x<='0'; y<='1';

wait for 100 ns;

x<='1'; y<='0';

wait for 100 ns;

x<='1'; y<='1';

wait for 100 ns;

- SOURCE CODE

use IEEE.STD_LOGIC_1164.ALL;

entity halfa is

Port ( x : in STD_LOGIC;

y : in STD_LOGIC;

sum : out STD_LOGIC;

cout : out STD_LOGIC);

end halfa;

architecture Behavioral of halfa is

begin

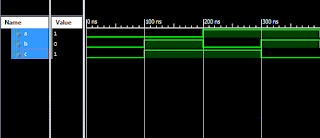

sum<= x xor y;

cout<= x and y;

end Behavioral;

- TESTBENCH

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY h1_tb IS

END h1_tb;

ARCHITECTURE behavior OF h1_tb IS

-- Component Declaration for

the Unit Under Test (UUT)

COMPONENT halfa

PORT(

x : IN STD_LOGIC;

y : IN STD_LOGIC;

sum : OUT STD_LOGIC;

cout : OUT STD_LOGIC

);

END COMPONENT;

--Inputs

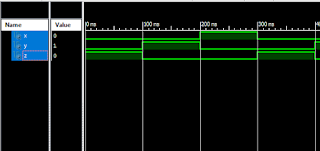

signal x : STD_LOGIC := '0';

signal y : STD_LOGIC := '0';

--Outputs

signal sum : STD_LOGIC;

signal cout : STD_LOGIC;

BEGIN

-- Instantiate the

Unit Under Test (UUT)

uut: halfa PORT MAP (

x => x,

y => y,

sum => sum,

cout => cout

);

-- Stimulus process

stim_proc: process

begin

x<='0';

y<='0';wait for 100 ns;

x<='0'; y<='1';

wait for 100 ns;

x<='1'; y<='0';

wait for 100 ns;

x<='1'; y<='1';

wait for 100 ns;

end process;

END;