The following is the VHDL code for D flip flop:

- Source Code

entity dff1 is

Port ( d : in STD_LOGIC;

reset : in STD_LOGIC;

CLOCK: in STD_LOGIC;

q : out STD_LOGIC

);

end dff1;

architecture Behavioral of dff1 is

begin

process(CLOCK)

begin

if ((CLOCK = '1') and CLOCK'EVENT) then

Q <= D after 5 ns;

end if;

end process;

end Behavioral;

- Test Bench

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY dff_tb IS

END dff_tb;

ARCHITECTURE behavior OF dff_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT dff1

PORT(

d : IN std_logic;

reset : IN std_logic;

CLOCK : IN std_logic;

q : OUT std_logic

);

END COMPONENT;

--Inputs

signal d : std_logic := '0';

signal reset : std_logic := '0';

signal CLOCK : std_logic := '0';

--Outputs

signal q : std_logic;

-- Clock period definitions

-- constant CLOCK_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: dff1 PORT MAP (

d => d,

reset => reset,

CLOCK => CLOCK,

q => q

);

-- Clock process definitions

CLOCK_process :process

begin

CLOCK <= '0';

wait for 50ns;

CLOCK <= '1';

wait for 50ns;

end process;

-- Stimulus process

stim_proc: process

begin

d<='1';

wait for 100ns;

d<='0';

wait for 100ns;

end process;

END;

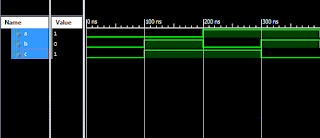

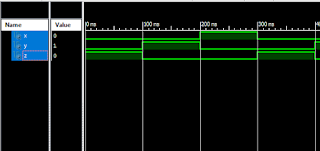

Output: